Home /

Expert Answers /

Computer Science /

1-assume-a-cpu-has-a-3-level-cache-and-a-dram-off-chip-main-memory-if-l1-cache-hit-is-2-cycles-co-pa457

(Solved): 1. Assume a CPU has a 3-level cache and a DRAM off-chip main memory. If L1 cache hit is 2 cycles (co ...

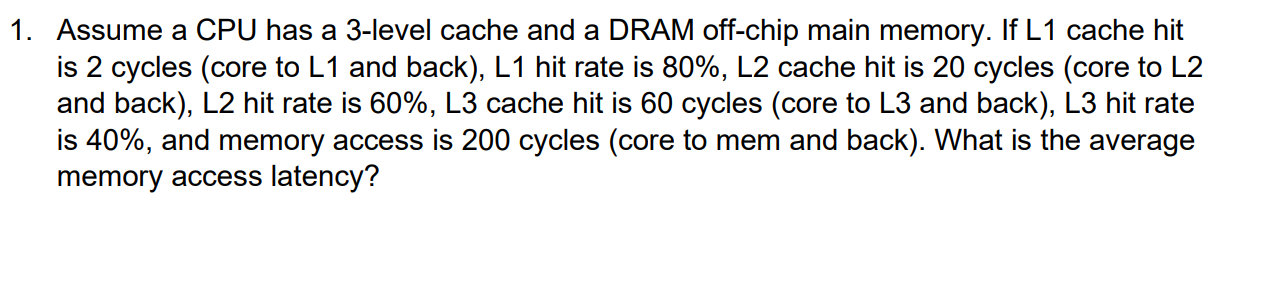

1. Assume a CPU has a 3-level cache and a DRAM off-chip main memory. If L1 cache hit is 2 cycles (core to L 1 and back), L 1 hit rate is \( 80 \% \), L 2 cache hit is 20 cycles (core to L2 and back), L2 hit rate is \( 60 \% \), L3 cache hit is 60 cycles (core to L3 and back), L3 hit rate is \( 40 \% \), and memory access is 200 cycles (core to mem and back). What is the average memory access latency?