(Solved): parameter no=37 (100 points) Considering (no+21)_(10)=(abcdefg)_(2), design a synchronous sequence ...

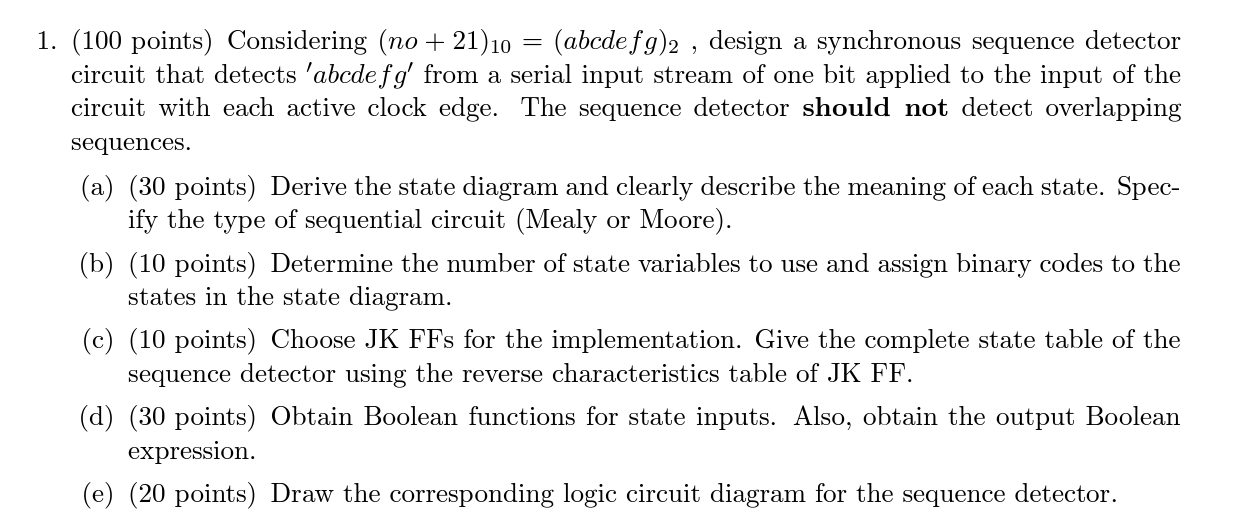

parameter no=37 (100 points) Considering (no+21)_(10)=(abcdefg)_(2), design a synchronous sequence detector circuit that detects 'abcdefg' from a serial input stream of one bit applied to the input of the circuit with each active clock edge. The sequence detector should not detect overlapping sequences. (a) (30 points) Derive the state diagram and clearly describe the meaning of each state. Spec- ify the type of sequential circuit (Mealy or Moore). (b) (10 points) Determine the number of state variables to use and assign binary codes to the states in the state diagram. (c) (10 points) Choose JK FFs for the implementation. Give the complete state table of the sequence detector using the reverse characteristics table of JK FF. (d) (30 points) Obtain Boolean functions for state inputs. Also, obtain the output Boolean expression. (e) (20 points) Draw the corresponding logic circuit diagram for the sequence detector.