Home /

Expert Answers /

Electrical Engineering /

q-1-given-that-x-is-a-4-bit-signed-number-represented-using-2-39-s-complement-representation-it-is-pa691

(Solved): Q.1. Given that X is a 4-bit signed number represented using 2's complement representation. It is ...

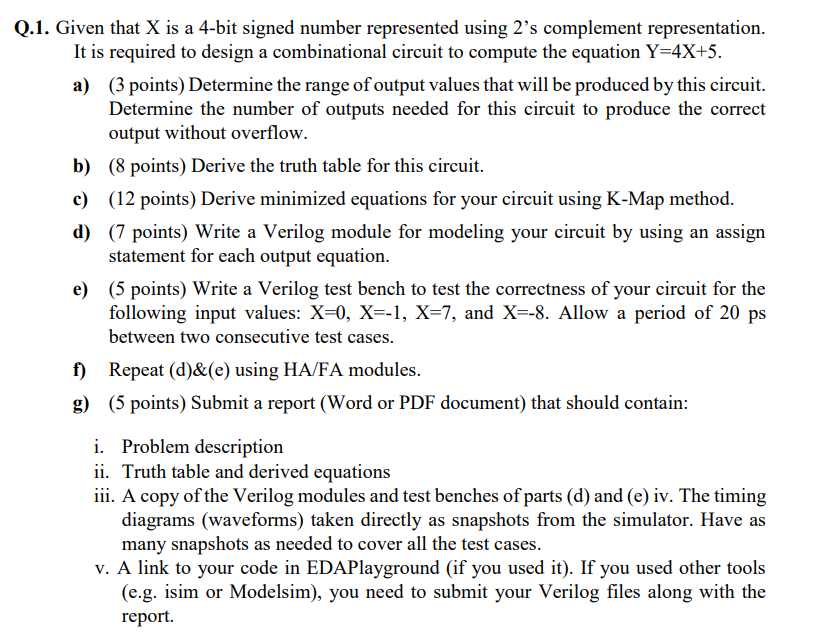

Q.1. Given that X is a 4-bit signed number represented using 2's complement representation. It is required to design a combinational circuit to compute the equation Y=4X+5. a) (3 points) Determine the range of output values that will be produced by this circuit. Determine the number of outputs needed for this circuit to produce the correct output without overflow. b) (8 points) Derive the truth table for this circuit. c) (12 points) Derive minimized equations for your circuit using K-Map method. d) (7 points) Write a Verilog module for modeling your circuit by using an assign statement for each output equation. e) (5 points) Write a Verilog test bench to test the correctness of your circuit for the following input values: X=0, x=-1, X=7, and X=-8. Allow a period of 20 ps between two consecutive test cases. f) Repeat (d)&(e) using HA/FA modules. g) (5 points) Submit a report (Word or PDF document) that should contain: i. Problem description ii. Truth table and derived equations iii. A copy of the Verilog modules and test benches of parts (d) and (e) iv. The timing diagrams (waveforms) taken directly as snapshots from the simulator. Have as many snapshots as needed to cover all the test cases. V. A link to your code in EDAPlayground (if you used it). If you used other tools (e.g. isim or Modelsim), you need to submit your Verilog files along with the report.

Expert Answer

Answer: a) The range of the output is 7 bits. We require 3 bits to represent 5 and X is a 4 bit signed number for storing the produ