(Solved): Refer to the diagram above for this question. The flip-flop FF2 has a hold time requirement of 100 ...

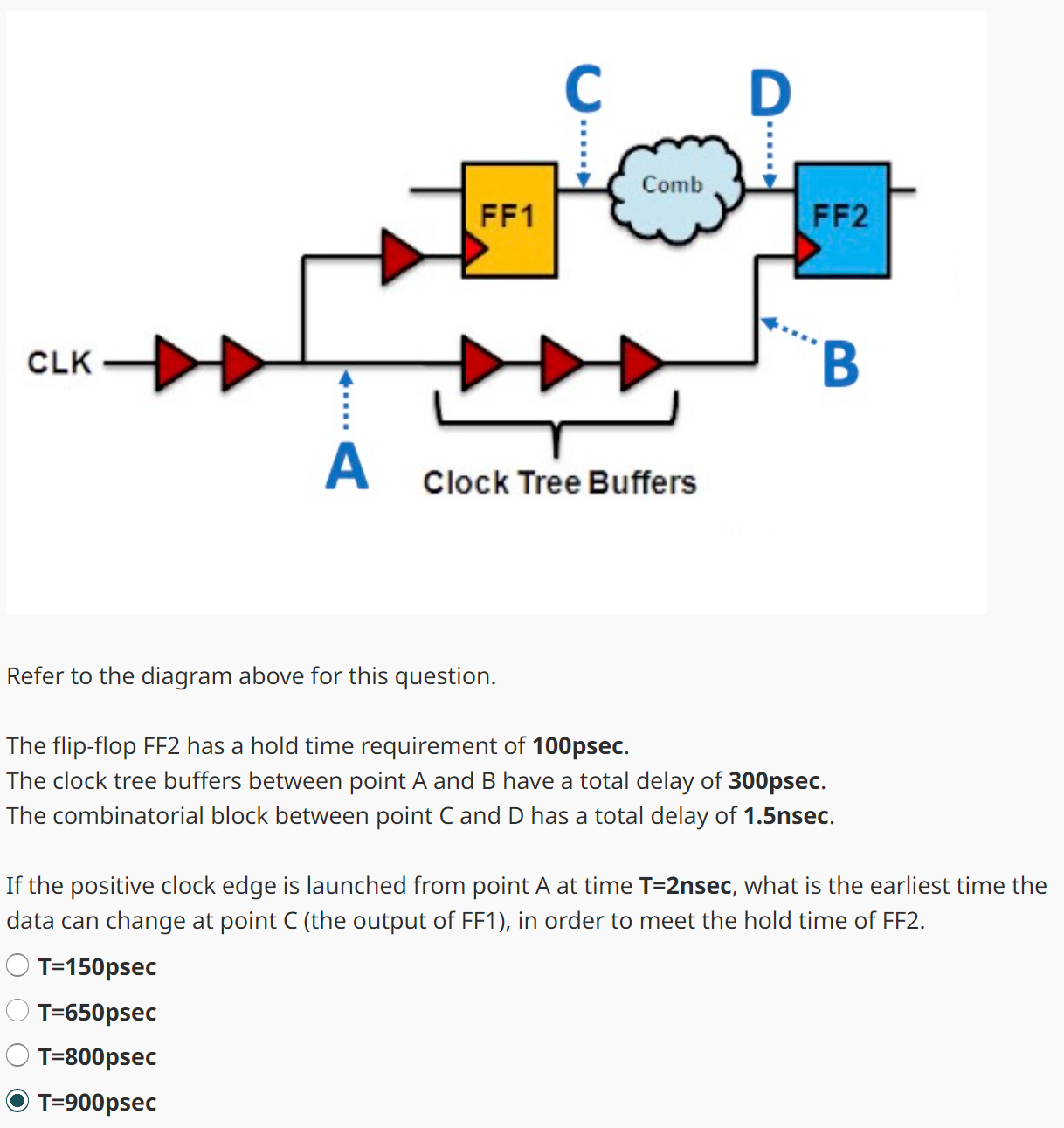

Refer to the diagram above for this question. The flip-flop FF2 has a hold time requirement of 100 psec. The clock tree buffers between point A and B have a total delay of 300psec. The combinatorial block between point

Cand

Dhas a total delay of

1.5nsec. If the positive clock edge is launched from point

Aat time

T=2nsec, what is the earliest time the data can change at point C (the output of FF1), in order to meet the hold time of FF2.

T=150psec

T=650psec

T=800psec

T=900psec