Home /

Expert Answers /

Electrical Engineering /

we-are-designing-a-3-bit-synchronous-counter-for-a-clock-input-in-which-the-input-clock-drives-al-pa643

(Solved): We are designing a 3-bit Synchronous Counter for a clock input, in which the input clock drives al ...

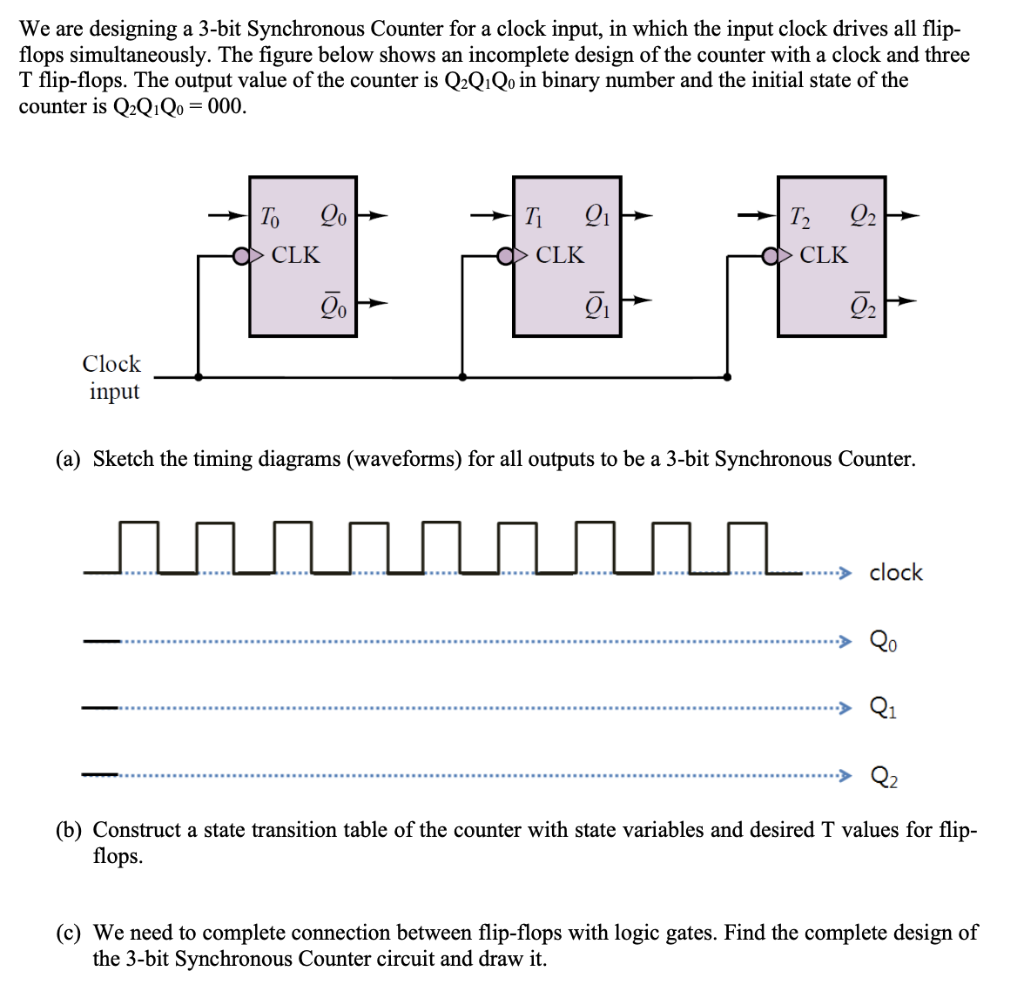

We are designing a 3-bit Synchronous Counter for a clock input, in which the input clock drives all flip- flops simultaneously. The figure below shows an incomplete design of the counter with a clock and three T flip-flops. The output value of the counter is Q2QQ in binary number and the initial state of the counter is Q2Q1Q0 = 000. To T? Q T2 22 C CLK C CLK CLK ??? Q 2? Clock input (a) Sketch the timing diagrams (waveforms) for all outputs to be a 3-bit Synchronous Counter. non- clock (b) Construct a state transition table of the counter with state variables and desired T values for flip- flops. (c) We need to complete connection between flip-flops with logic gates. Find the complete design of the 3-bit Synchronous Counter circuit and draw it.